Contact: mketchen@octevue.com

Reduce risk and optimize investment in technology development

As CMOS nears the limits of scaling the costs of adding enhancements at the present node and developing the next node are becoming extremely expensive. In the end it will be a cost performance proposition,

not the laws of physics that will determine the end of scaling. In the meantime it is essential to have a bullet-proof methodology in place to quantatatively assess the performance gains that specific enhancements and scaling scenarios can be expected to deliver. It is equally important to be able to perform apples-to-apples comparisons of CMOS with competing alternative technologies as they emerge.

As CMOS nears the limits of scaling the costs of adding enhancements at the present node and developing the next node are becoming extremely expensive. In the end it will be a cost performance proposition,

not the laws of physics that will determine the end of scaling. In the meantime it is essential to have a bullet-proof methodology in place to quantatatively assess the performance gains that specific enhancements and scaling scenarios can be expected to deliver. It is equally important to be able to perform apples-to-apples comparisons of CMOS with competing alternative technologies as they emerge.

Throughout his career as a scientist and manager at IBM Dr. Ketchen has been extensively involved in technology performance assessments across a range of technologies and enhancements from silicon to superconducting Josephson technology comparisons in the early 1980s to bulk CMOS versus partially depleted SOI assessments over the past decade, and most recently in sorting through a variety of superconducting qubit designs for quantum computing. He brings to the table a wealth of experience in charting viable courses through the technology, device , design landscape.

"CMOS Test and Evaluation: A Physical Perspective"

From the back cover: This book extends test structure applications described in Microelectronic Test Structures for CMOS Technology

(Springer 2011) to digital CMOS product chips. Intended for engineering students and professionals,

this book provides a single comprehensive source for evaluating CMOS technology and product test data from a basic knowledge

of the physical behavior of the constituent components. Elementary circuits that exhibit key properties of complex

CMOS chips are simulated and analyzed, and an integrated view of design, test and characterization is developed.

Appropriately designed circuit monitors embedded in the CMOS chip serve to correlate CMOS technology models and circuit design tools

to the hardware and also aid in test debug. Impact of silicon process variability, reliability,

and power and performance sensitivities to a range of product application conditions are described.

Circuit simulations exemplify the methodologies presented, and problems are included at the end of the chapters.

Authors: Manjul Bhushan and Mark B. Ketchen

Springer, published December 2014.

Available in hardcover and ebook

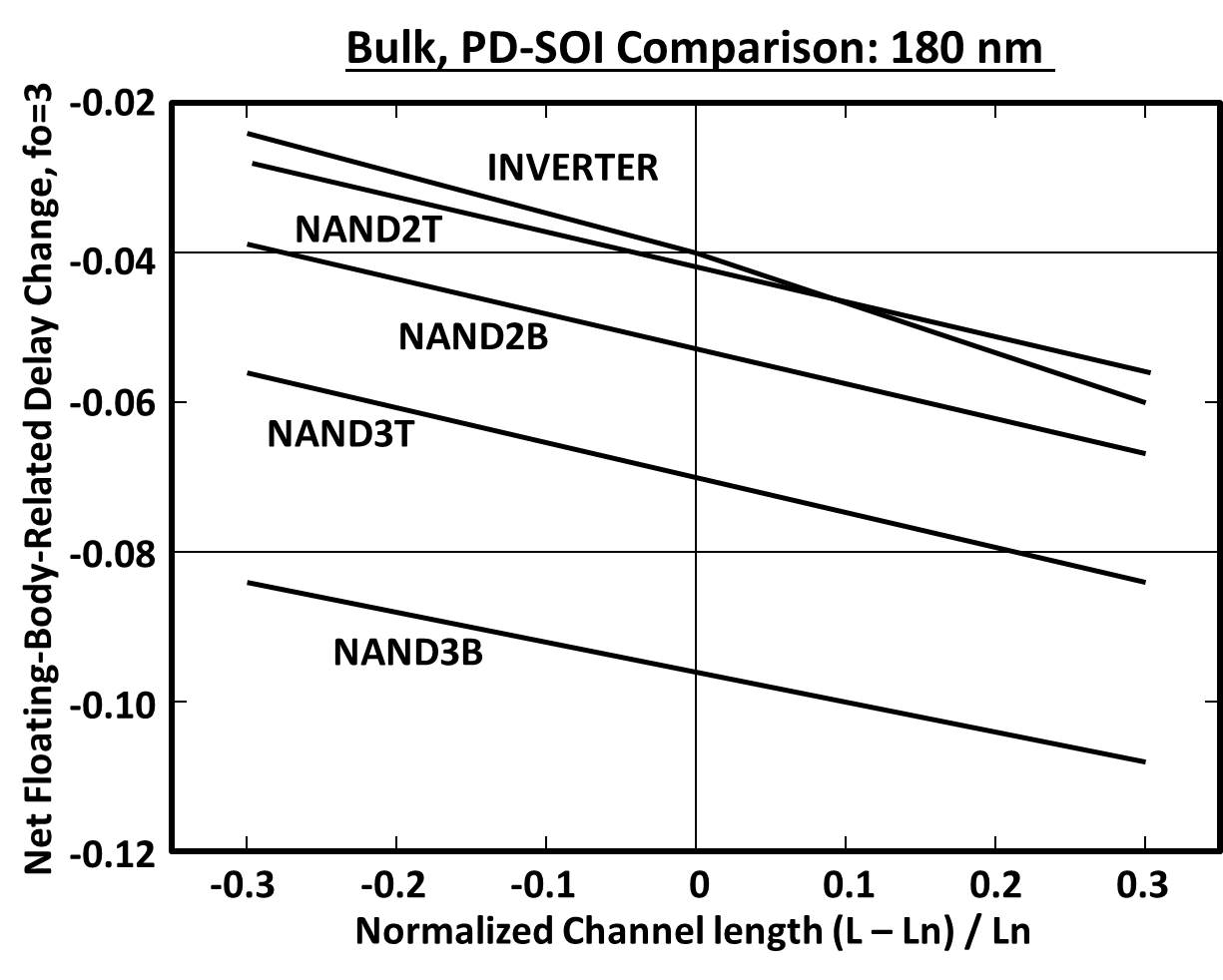

1. Competitive advantage of SOI from dynamic threshold shifts and reduced capacitance

Ketchen MB (2003). Proceedings 2003 international symposium on VLSI technology, systems and applications, 2003, pp 129-132

2. Anomalous history behavior in stacked PD SOI gates

Ketchen MB, Bhushan M (2003). Proceedings of the 2003 IEEE international SOI conference, 2003, pp 168-169

3. Deep sub-micron low-Tc Josephson technology: the opportunities and the challenges

Ketchen MB (1993). IEEE Trans on Appl Sup 3: 2586-2593

4. Point Defect Yield Model for Wafer Scale Integration

Ketchen MB (1985). IEEE Ckt and Dev Mag 1: 24-34